Circuit

Processing-in-memory

Neural Processor

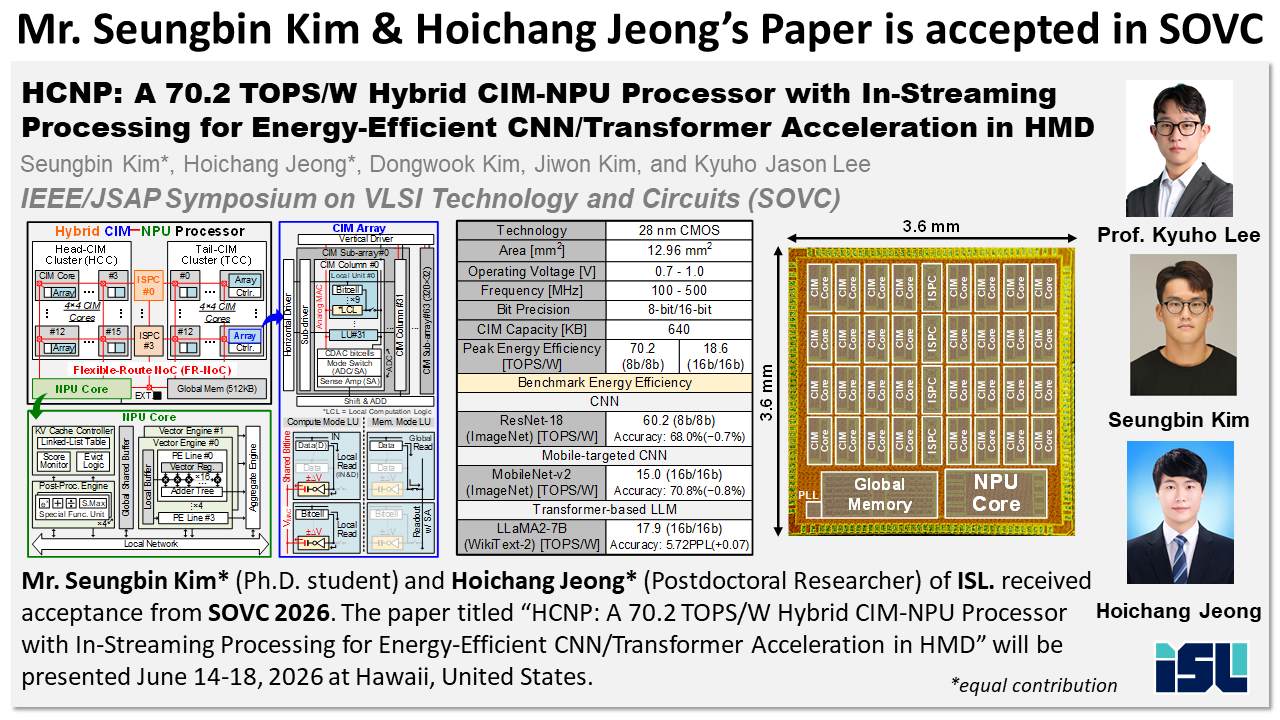

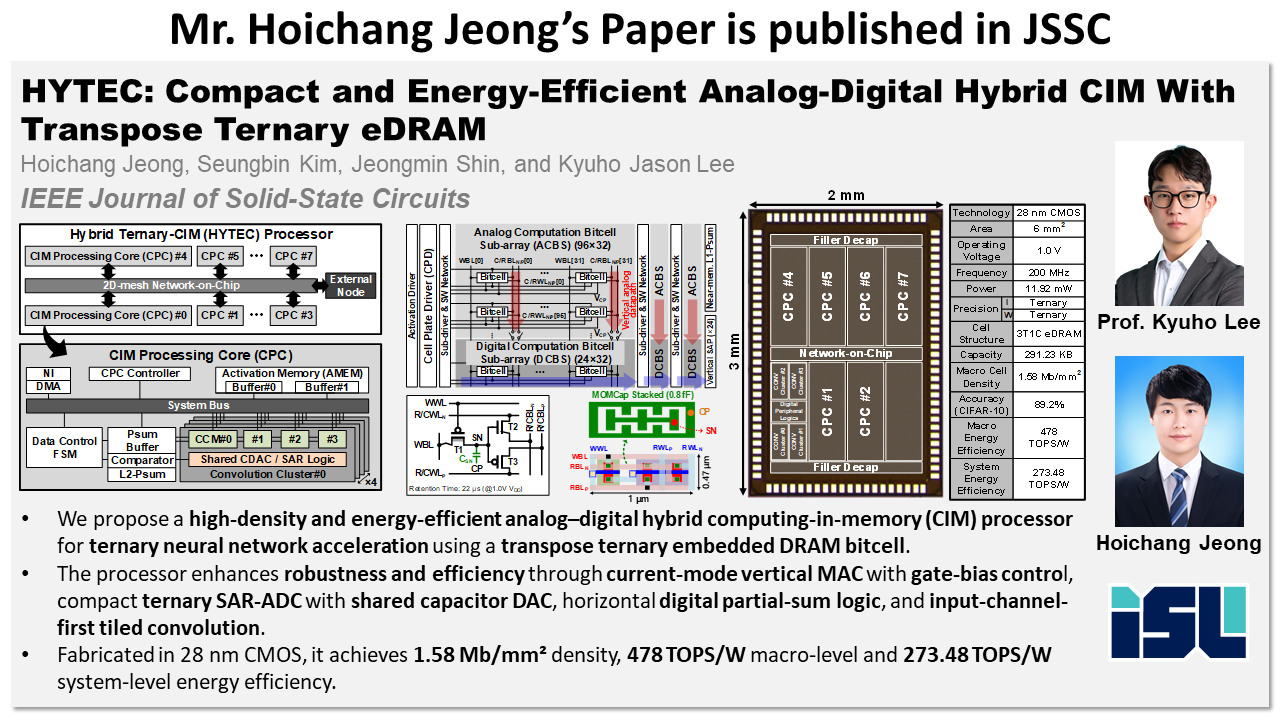

HCNP: A 70.2 TOPS/W Hybrid CIM-NPU Processor with In-Streaming Processing for Energy-Efficient CNN/Transformer Acceleration in HMD

IEEE/JSAP Symposium on VLSI Technology and Circuits, Jun. 2026

Seungbin Kim*, Hoichang Jeong*, Dongwook Kim, Jiwon Kim, and Kyuho Jason Lee (*equal contribution)